Alors que les technologies de l’intelligence artificielle, du calcul haute performance et de la réalité virtuelle/augmentée continuent de repousser les limites, la demande en mémoires ultra-rapides et ultra-performantes ne cesse de croître. C’est dans ce contexte que l’HBM4 (High Bandwidth Memory 4) fait son entrée, promettant des avancées majeures en termes de bande passante, de densité et d’efficacité énergétique.

Qu’est-ce que l’HBM4 ?

L’HBM4 est la quatrième itération de la mémoire HBM (High Bandwidth Memory), une technologie de mémoire vive 3D empilée, destinée aux charges de travail gourmandes en données. Développée par un consortium mené par AMD, Samsung et SK Hynix, elle succède à l’HBM3 et promet des améliorations spectaculaires.

Les principales caractéristiques annoncées de l’HBM4 sont :

- Interface mémoire ultra-large de 2048 bits (contre 1024 bits pour l’HBM3)

- Bande passante stupéfiante de 1,6 To/s par stack

- Vitesse de transfert des données de 6,4 Gb/s par broche

- Densité allant jusqu’à 64 Go par stack

- Consommation d’énergie réduite par rapport à l’HBM3

Une interface deux fois plus large

L’un des changements les plus marquants de l’HBM4 réside dans son interface mémoire ultra-large de 2048 bits, deux fois supérieure à celle de l’HBM3. Cette augmentation drastique de la largeur de bande permet de doubler le débit de données brutes, répondant ainsi aux besoins toujours croissants en bande passante des charges de travail d’IA, de data center et de calcul scientifique.

Des performances et une efficacité énergétique accrues

Outre sa large interface, l’HBM4 vise à repousser les limites de la bande passante avec un débit de 1,6 To/s par stack, grâce à une vitesse de transfert de 6,4 Gb/s par broche. Malgré ces performances stratosphériques, l’HBM4 devrait également faire des progrès en matière d’efficacité énergétique, une préoccupation majeure dans les datacenters et les systèmes embarqués.

Une densité démultipliée

Avec une densité pouvant atteindre 64 Go par stack, l’HBM4 va permettre de concentrer des quantités gigantesques de mémoire à très haute bande passante à proximité immédiate des puces de calcul accélérées. Cette capacité élevée, combinée au faible encombrement et à la faible consommation de l’HBM, en fait la solution idéale pour les systèmes compacts haute performance.

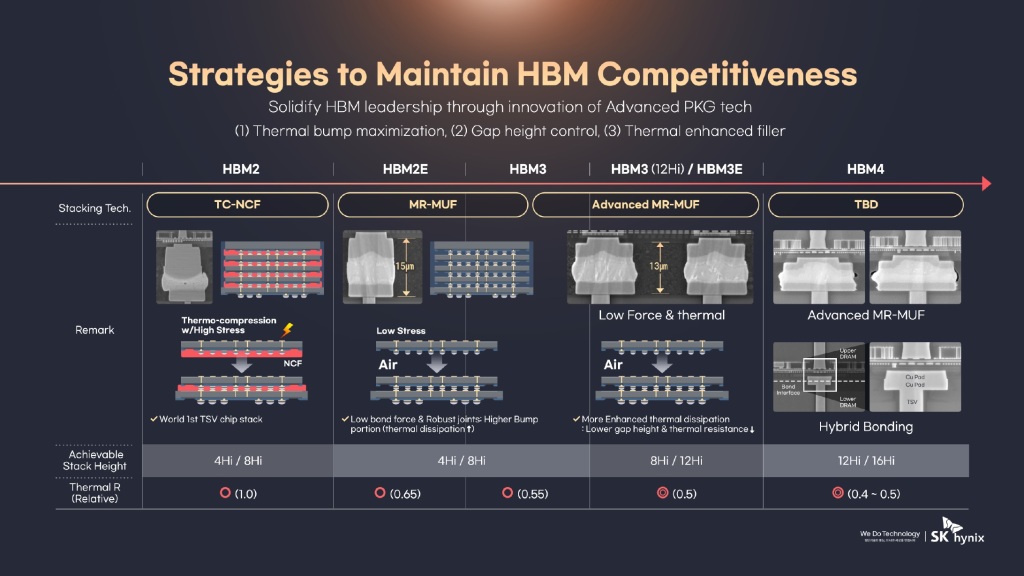

Nouvelles techniques d’assemblage

Pour atteindre ces niveaux de performances inédits, les fabricants d’HBM4 comme Samsung vont devoir repousser les limites des techniques d’assemblage 3D. Samsung développe ainsi des adhésifs non conducteurs (NCP) optimisés pour les hautes températures, ainsi que le hybrid bonding qui permettra d’empiler plus de couches de mémoire.

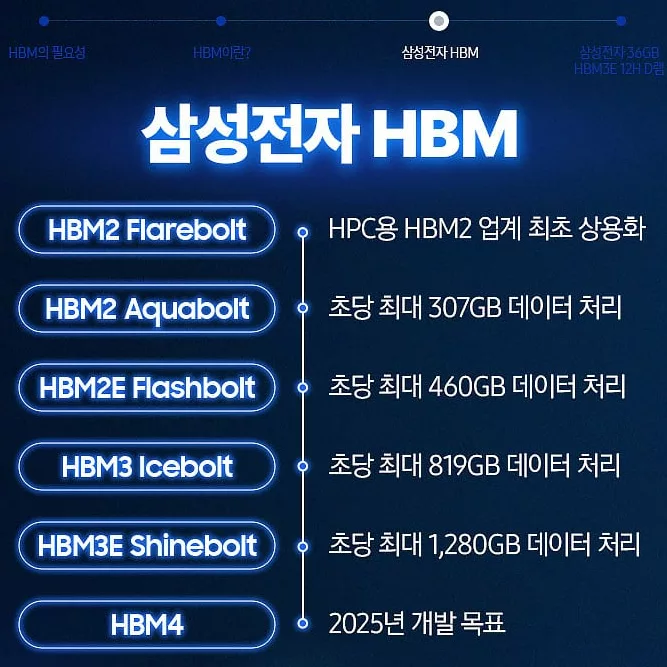

Quand arrivera l’HBM4 sur le marché ?

Bien que les annonces de performances soient déjà alléchantes, l’adoption à grande échelle de l’HBM4 n’est pas prévue avant 2025 au moins. Les principaux fabricants comme Samsung, SK Hynix et Micron prévoient de commencer l’échantillonnage de l’HBM3e, l’itération précédant l’HBM4, dès début 2024, avec une production de masse fin 2024.

NVIDIA devrait être l’un des premiers clients de l’HBM4, avec son intégration prévue dans l’architecture GPU pour AI en 2025. D’autres acteurs comme les concepteurs de puces d’IA et les fabricants de systèmes HPC devraient rapidement suivre.

L’HBM4 promet ainsi d’apporter une nouvelle vague de puissance de calcul aux applications les plus exigeantes, des supercalculateurs à l’intelligence artificielle générative, en passant par la réalité virtuelle et bien d’autres. Une avancée de taille pour les systèmes haute performance de demain.