En 2020, nous vous annoncions que TSMC, leader mondial de la fabrication de semi-conducteurs, se lançait à pleine vitesse vers le 2 nm. Aujourd’hui, 5 ans après, nous sommes de retour pour confirmer des avancées majeures dans le développement de son procédé de gravure en 2 nm (N2).

Prévu pour entrer en production de masse dès 2025, ce nouveau nœud technologique promet des performances inédites, notamment grâce à l’introduction des transistors nanofeuille de première génération.

Des performances et une efficacité énergétique améliorées

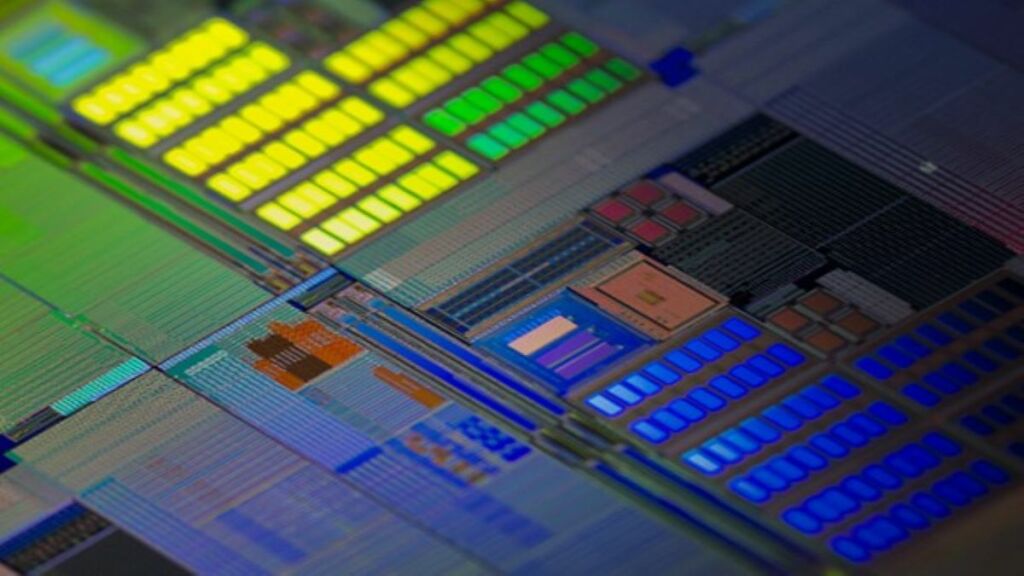

Le procédé N2 introduit une nouvelle architecture GAA (Gate-All-Around), qui devrait significativement réduire la consommation énergétique tout en augmentant la densité des transistors. Cela répondra aux besoins croissants d’applications exigeantes comme l’informatique haute performance et l’intelligence artificielle. De plus, TSMC a développé des innovations supplémentaires, telles que des couches métalliques interconnectées à faible résistance et des condensateurs MiM (Metal-insulator-Metal), pour maximiser l’efficacité.

Une adoption déjà en cours par les clients majeurs

Selon les déclarations de TSMC, plusieurs clients ont déjà complété les conceptions de leurs IP en 2 nm et ont entamé les phases de validation. Ces progrès renforcent la position de TSMC face à la demande croissante du marché pour des solutions plus performantes que celles basées sur le 3 nm.

Présentation officielle en décembre 2024

TSMC prévoit de dévoiler plus de détails techniques lors de la conférence IEDM en décembre 2024. L’un des points forts attendus est la réduction de la taille des cellules SRAM, désormais de 0,0175 μm², offrant des améliorations significatives pour les CPU, GPU et SoC modernes nécessitant des capacités accrues de mémoire cache.

Avec ces avancées, TSMC continue de démontrer son rôle de pionnier dans l’industrie des semi-conducteurs, consolidant ainsi sa domination sur le marché des technologies de pointe.