La mémoire des serveurs IA change de forme, et pas seulement de cadence. Rambus prend position sur un terrain encore émergent avec une première brique pensée pour faire entrer la LPDDR5X modulaire dans le datacenter.

Rambus a présenté un chipset SOCAMM2 destiné aux modules mémoire serveur basés sur la LPDDR5X. L’idée est de répondre aux nouvelles contraintes des plateformes IA, où la consommation, la densité, l’encombrement sur carte et la capacité d’évolution de la mémoire deviennent aussi critiques que la bande passante brute.

SOCAMM2, une alternative modulaire à la LPDDR soudée

SOCAMM2, pour Small Outline Compression Attached Memory Module, remplace la mémoire LPDDR soudée par des modules détachables et évolutifs. L’approche conserve les avantages énergétiques de la LPDDR tout en ajoutant une forme de maintenabilité plus conforme aux attentes du monde serveur.

Rambus présente ce lancement comme la première étape d’une feuille de route plus large autour de solutions serveur à base de LPDDR. Le fabricant explique travailler avec ses partenaires de l’écosystème pour accompagner de nouvelles architectures mémoire adaptées aux charges IA dans les infrastructures de datacenter.

Le groupe souligne aussi que cette famille vient compléter son catalogue de chipsets d’interface mémoire pour les modules DDR5 et LPDDR5 conformes aux standards JEDEC.

Un chipset taillé pour la LPDDR5X en environnement serveur

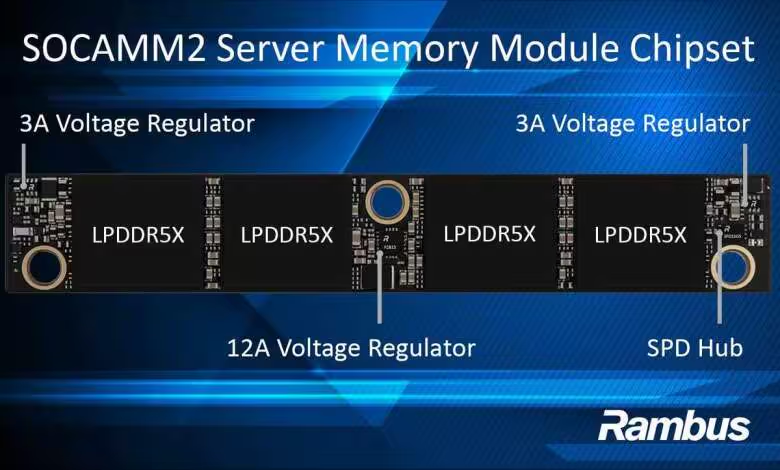

Le chipset Rambus SOCAMM2 est conçu pour assurer les fonctions de contrôle, de télémétrie et d’alimentation nécessaires aux modules mémoire SOCAMM2 standardisés par la JEDEC. L’objectif est de garantir un fonctionnement fiable et sobre dans des serveurs IA où les contraintes thermiques et électriques deviennent rapidement limitantes.

Sur le plan technique, la solution prend en charge des modules LPDDR5X jusqu’à 9,6 Gb/s. Rambus mentionne la présence d’un SPD Hub pour l’identification du module, la configuration et la télémétrie, ainsi que des régulateurs de tension de 12 A et 3 A pour une conversion d’alimentation locale plus efficace.

Micron et IDC voient un signal pour l’écosystème

Rami Sethi, SVP et general manager de l’activité Memory Interface Chips chez Rambus, estime que la mémoire est devenue l’un des principaux leviers de performance, d’efficacité et de montée en charge dans les architectures IA. Il précise aussi que d’autres solutions serveur basées sur la LPDDR sont déjà en développement.

Chez Micron, Praveen Vaidyanathan, vice president et general manager de Cloud Memory Products, voit dans SOCAMM2 une étape importante vers une mémoire connectée au CPU, plus efficace et plus scalable pour la prochaine vague de serveurs IA. IDC, par la voix de Soo Kyoum Kim, associate VP memory semiconductors, estime de son côté que des architectures comme SOCAMM2 répondent directement aux limites actuelles en matière de puissance, de bande passante et de densité.

Ce mouvement est intéressant parce qu’il cherche à concilier deux mondes longtemps opposés : l’efficacité énergétique de la LPDDR, traditionnellement réservée aux usages embarqués et mobiles, et la logique de serviceabilité imposée par le serveur. Si l’écosystème suit, SOCAMM2 pourrait ouvrir une voie crédible pour densifier la mémoire des nœuds IA sans continuer à alourdir leur budget énergétique.

Source : TechPowerUp