La DRAM classique approche de ses limites, et certains acteurs cherchent déjà la sortie par le haut, au sens littéral. NEO Semiconductor affirme avoir validé sur silicium sa 3D X-DRAM, avec des résultats qui placent la mémoire empilée au centre des prochaines architectures IA.

Un premier jalon concret pour la 3D X-DRAM

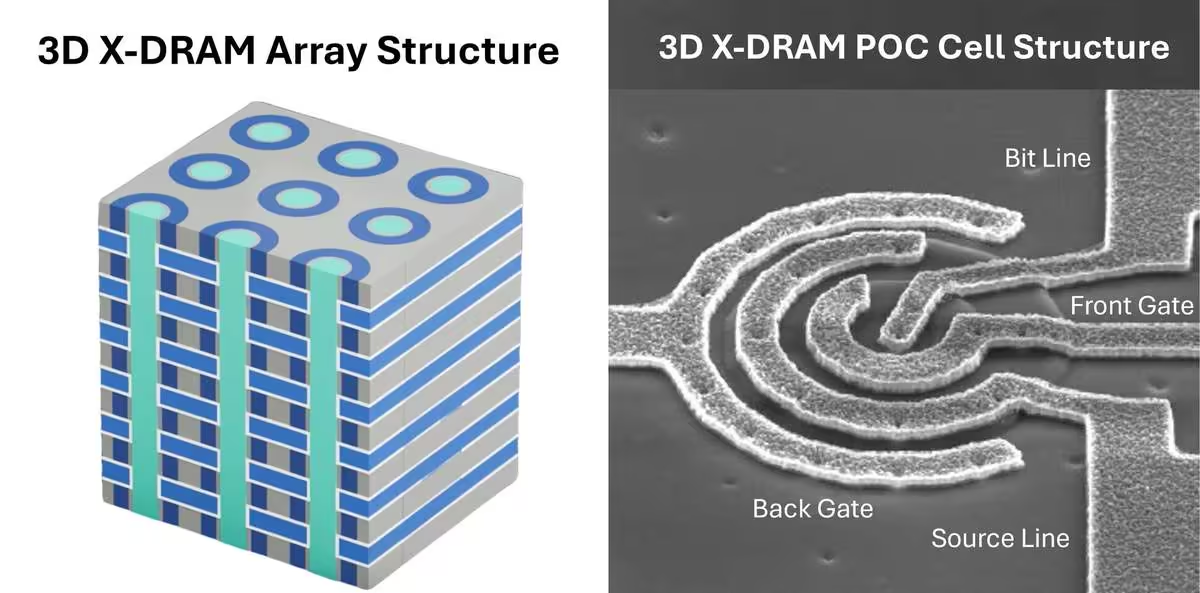

La société a présenté un proof-of-concept développé avec la National Yang Ming Chiao Tung University à Taïwan, via son Industry-Academia Innovation School, puis fabriqué et testé au NIAR-TSRI, le National Institutes of Applied Research-Taiwan Semiconductor Research Institute. L’intérêt de l’annonce tient surtout à un point : ces puces de test montrent que la technologie peut être produite à partir de l’infrastructure existante de la 3D NAND, en réutilisant équipements, matériaux et procédés déjà maîtrisés.

NEO insiste sur le fait que la 3D NAND a déjà dépassé les 300 couches en production. En clair, la société veut faire valoir qu’une filière industrielle capable de monter très haut en vertical existe déjà, ce qui pourrait accélérer l’arrivée d’une DRAM 3D à forte densité sans repartir de zéro.

Des chiffres solides sur le papier

Les résultats électriques communiqués sont ambitieux : une latence en lecture et en écriture inférieure à 10 ns, une rétention des données supérieure à 1 seconde à 85 °C, soit 15 fois mieux que le standard JEDEC de 64 ms, ainsi qu’une résistance aux perturbations bit-line et word-line également supérieure à 1 seconde à 85 °C. L’endurance est annoncée au-delà de 10^14 cycles.

Pour Andy Hsu, fondateur et CEO de NEO Semiconductor, ces mesures valident une nouvelle voie de mise à l’échelle pour la DRAM, avec à la clé plus de densité, des coûts potentiellement plus bas et une meilleure efficacité énergétique pour les charges IA. L’entreprise dit déjà discuter avec plusieurs acteurs majeurs de la mémoire et des semi-conducteurs autour de co-développements et d’un modèle basé sur la licence et le partenariat.

Soutien industriel, financement et prochaine étape

L’annonce s’accompagne d’un investissement stratégique mené par Stan Shih, fondateur et ancien chairman et CEO d’Acer, également ancien administrateur de TSMC pendant plus de 20 ans. NEO ne détaille pas le montant, mais précise que ce financement a déjà servi au développement du POC et qu’il doit désormais soutenir la mise en œuvre au niveau array, la conception de puces de test multicouches et l’approfondissement des discussions avec les grands noms du secteur.

Le projet a aussi reçu le soutien public de Jack Sun, Senior Vice President de la NYCU, doyen de l’IAIS et ancien CTO de TSMC, qui met en avant la faisabilité du concept dans des conditions réelles de procédé silicium. De son côté, Jeongdong Choe, Senior Technical Fellow et SVP chez TechInsights, voit dans cette démonstration un jalon important au moment où la DRAM conventionnelle touche ses limites de scaling et où l’industrie se tourne vers des architectures 3D.

NEO prévoit de détailler davantage ces résultats lors du salon FMS: Future of Memory and Storage, prévu du 4 au 6 août 2026 au Santa Clara Convention Center, en Californie. Andy Hsu y donnera une keynote, tandis que l’entreprise exposera sur le stand n°507.

Le point clé, au-delà de l’effet d’annonce, reste la promesse d’une DRAM empilée exploitable avec des briques industrielles proches de la 3D NAND. Si cette compatibilité se confirme à grande échelle, la bataille de la mémoire pour l’IA pourrait se jouer autant sur la capacité à verticaliser la production que sur les performances brutes.

Source : TechPowerUp