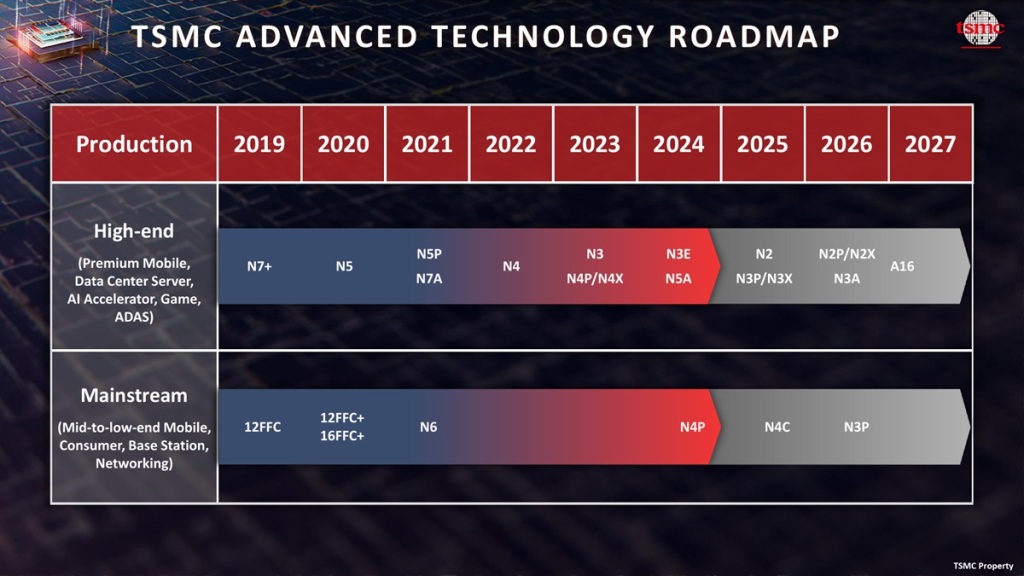

Lors du forum européen « Open Innovation Platform » (OIP), le géant taïwanais des semi-conducteurs TSMC a confirmé que le procédé A16 entrerait en production à la fin de l’année 2026. En parallèle, le procédé N2, une avancée majeure en nanotechnologie, débutera sa production de masse dès fin 2025. L’entreprise a souligné que son calendrier de développement des technologies avancées reste aligné sur sa feuille de route initiale.

Dans notre article précédent, TSMC accélère sa production N2 en 2 nm pour une commercialisation en 2025, nous avons détaillé l’arrivée imminente du procédé N2 et son impact potentiel sur l’industrie. Le lancement du A16 s’inscrit dans cette évolution et confirme l’engagement de TSMC à maintenir sa domination technologique.

Un calendrier ambitieux pour N2 et A16

D’après un rapport de Tom’s Hardware, plusieurs nouvelles technologies verront le jour entre fin 2025 et fin 2026. Ces procédés incluent le N2P, le N2X, et le très attendu A16. Bien que ces technologies ne soient pas introduites simultanément, TSMC garantit leur disponibilité pour une production en masse avant fin 2026.

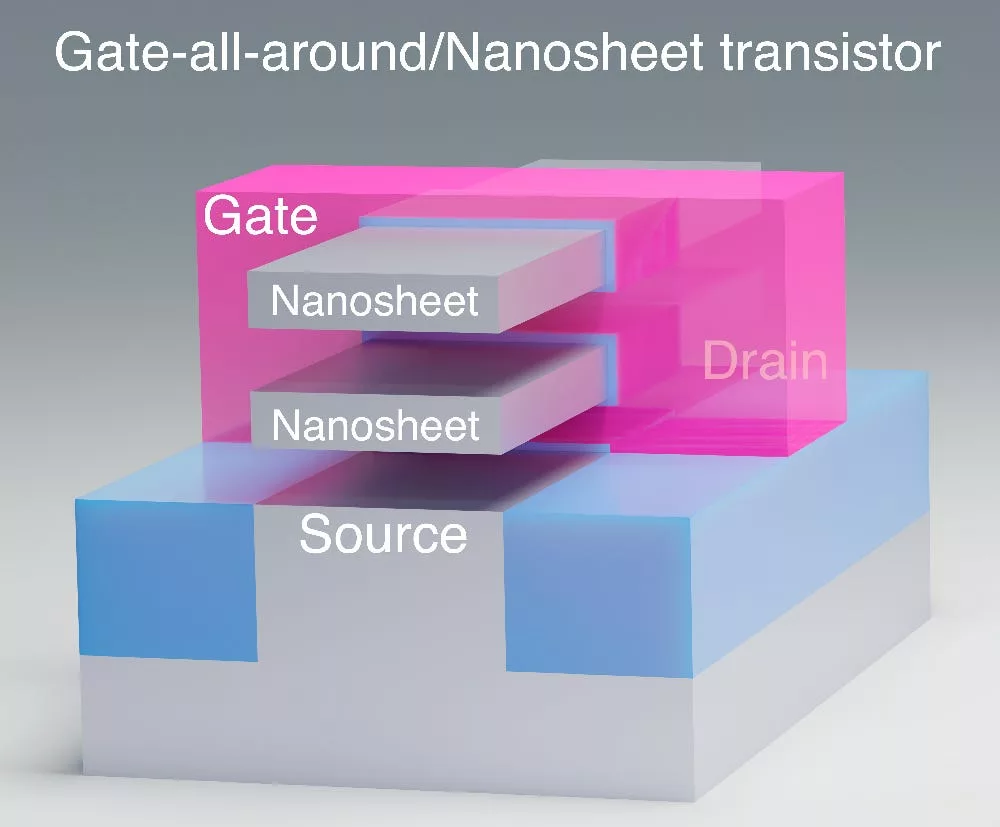

Les procédés N2P, N2X et A16 reposent sur une architecture GAA (Gate-All-Around), offrant des transistors de nouvelle génération. De plus, ils intégreront des condensateurs SHPMIM (High-Performance Metal-Insulator-Metal), renforçant leurs performances électriques.

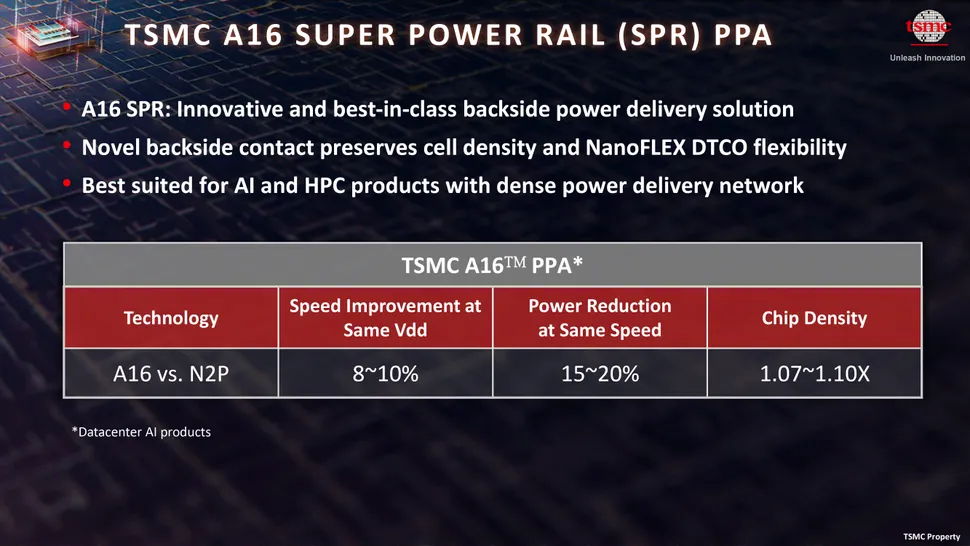

Procédé A16 : Efficacité accrue grâce à la technologie de rétro-alimentation

La grande nouveauté du procédé A16 réside dans l’utilisation de l’architecture Super Power Rail, une technologie de rétro-alimentation. Cette innovation libère de l’espace en surface, augmentant la densité logique tout en améliorant l’efficacité énergétique. Elle s’avère particulièrement adaptée aux produits de calcul haute performance (HPC).

Comparé au procédé N2P, l’A16 offre des améliorations notables :

- Une vitesse accrue de 8 à 10 % à tension égale.

- Une réduction de la consommation énergétique de 15 à 20 % pour des performances similaires.

- Une densité logique augmentée de 1,1 fois.

Dan Kochpatcharin, directeur de la gestion des infrastructures de conception chez TSMC, a décrit l’A16 comme une évolution du N2P enrichie par la technologie de rétro-alimentation. Cependant, il a précisé que cette avancée technique entraîne des défis thermiques supplémentaires. Ainsi, l’A16 sera principalement utilisé pour des applications spécifiques, notamment les puces destinées au calcul haute performance.

Analyse & Avis

L’annonce de TSMC s’inscrit dans une dynamique de compétitivité accrue sur le marché des semi-conducteurs. La transition vers les technologies GAA et la mise en œuvre de l’architecture Super Power Rail reflètent l’engagement de TSMC à repousser les limites en termes d’efficacité énergétique et de densité logique.

Cependant, les défis liés à la gestion thermique et aux coûts de production élevés pourraient limiter l’adoption à grande échelle de ces technologies. À court terme, leur intégration semble mieux adaptée aux besoins des centres de données et des applications HPC, où les performances justifient ces investissements.

Avec ce calendrier de production ambitieux, TSMC consolide sa position de leader et prépare la voie à une nouvelle génération de puces, répondant aux exigences croissantes de l’industrie technologique.