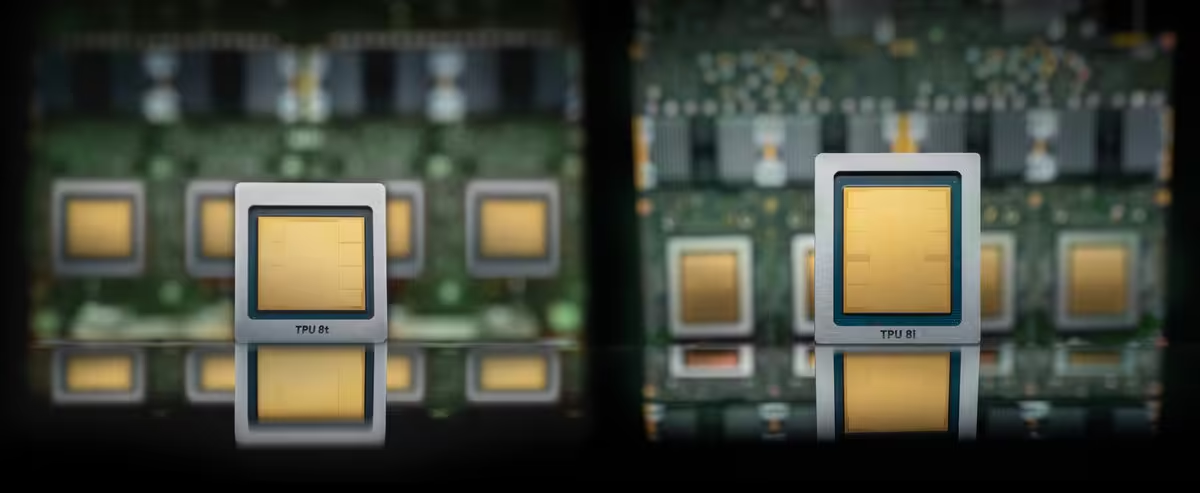

Deux puces au lieu d’une, et un message assez clair sur l’état du marché : l’IA ne se contente plus d’un accélérateur polyvalent. Google prépare ainsi sa huitième génération de TPU avec une séparation nette entre l’entraînement massif et l’inférence à faible latence.

Présentés à Google Cloud Next, les TPU 8t et TPU 8i doivent alimenter les supercalculateurs maison du groupe, pour couvrir aussi bien l’apprentissage de modèles de pointe que les charges d’inférence à grande échelle et les usages dits agentiques. Google rappelle au passage que ses TPU servent déjà depuis des années à faire tourner ses grands modèles, Gemini compris.

Deux architectures pour des contraintes qui divergent

Le choix le plus important n’est pas un chiffre brut, mais la spécialisation. Google explique avoir anticipé il y a plusieurs années la montée de la demande en inférence de production, puis l’arrivée d’agents capables d’enchaîner raisonnement, planification, exécution et apprentissage en boucle. De là, deux puces distinctes, développées avec Google DeepMind.

Le TPU 8t vise les charges d’entraînement très intensives en calcul, avec plus de débit de calcul et davantage de bande passante en scale-up. Le TPU 8i, lui, privilégie la bande passante mémoire pour les inférences les plus sensibles à la latence. Google précise que les deux puces restent polyvalentes, mais que cette spécialisation débloque des gains d’efficacité significatifs.

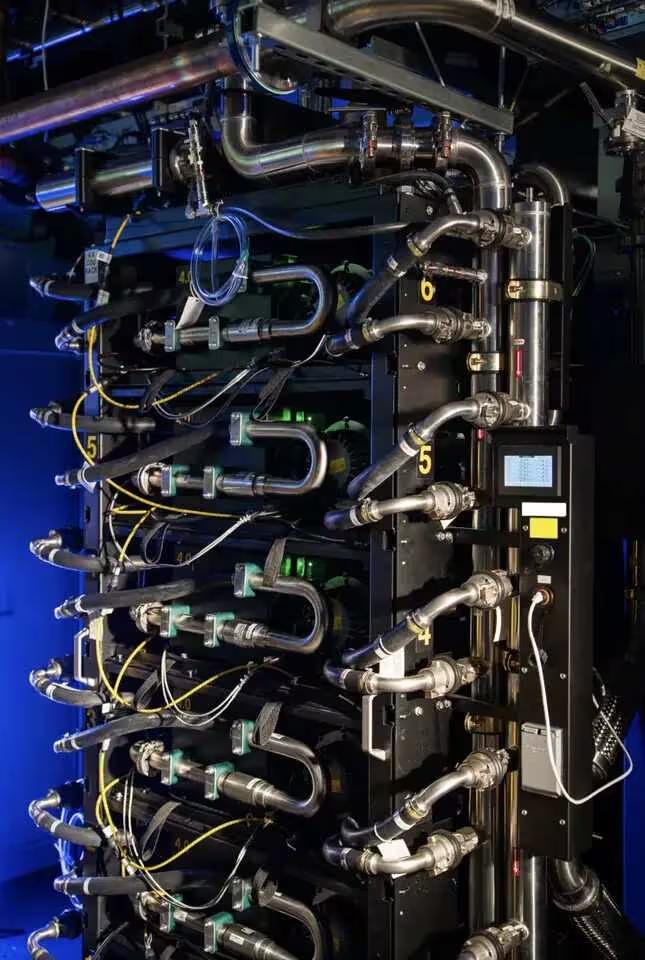

Le groupe inscrit aussi cette génération dans la continuité de plus de dix ans de développement TPU : formats numériques maison, refroidissement liquide, interconnexions propriétaires et co-conception entre silicium, réseau, logiciels et architectures de modèles. L’idée reste la même qu’à l’origine : optimiser l’ensemble de la pile plutôt qu’un composant isolé.

TPU 8t, la version entraînement à très grande échelle

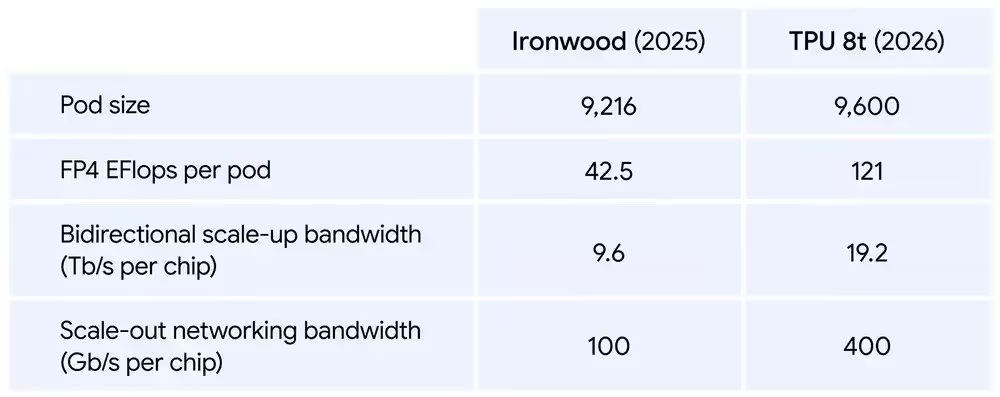

Google présente le TPU 8t comme une machine pensée pour ramener le cycle de développement des modèles frontier de plusieurs mois à quelques semaines. Au niveau système, un superpod TPU 8t peut désormais monter à 9 600 puces et 2 pétaoctets de mémoire partagée à haute bande passante, avec une bande passante inter-puces doublée par rapport à la génération précédente.

L’ensemble délivre jusqu’à 121 ExaFlops de calcul par superpod. Google annonce aussi un accès au stockage 10 fois plus rapide, combiné à TPUDirect pour injecter directement les données dans le TPU, ainsi qu’un nouveau réseau Virgo associé à JAX et Pathways pour viser une montée en charge quasi linéaire jusqu’à 1 million de puces dans un seul cluster logique.

La firme met également en avant le rendement réel de la machine, avec un objectif de plus de 97 % de goodput. Derrière ce terme, il s’agit du temps de calcul réellement utile, grâce à une télémétrie en temps réel sur des dizaines de milliers de puces, à la détection automatique des liens ICI défaillants, au reroutage sans interruption de tâche et à un système d’Optical Circuit Switching capable de reconfigurer le matériel sans intervention humaine.

TPU 8i, l’inférence optimisée pour les agents et les modèles MoE

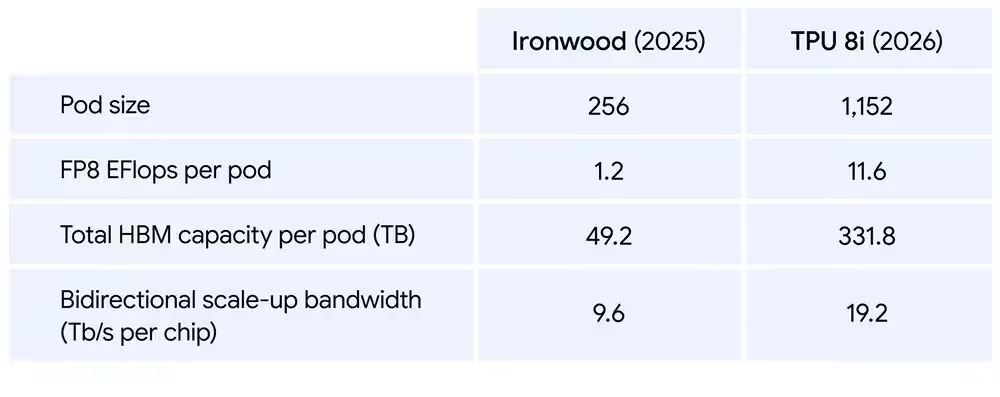

Le TPU 8i cible un autre problème : réduire les temps morts et la latence quand plusieurs agents spécialisés collaborent dans des flux complexes. Pour cela, Google évoque quatre évolutions majeures, à commencer par la mémoire. Chaque puce embarque 288 Go de mémoire à haute bande passante et 384 Mo de SRAM on-chip, soit 3 fois plus que sur la génération précédente, afin de garder l’ensemble de travail actif d’un modèle directement sur la puce.

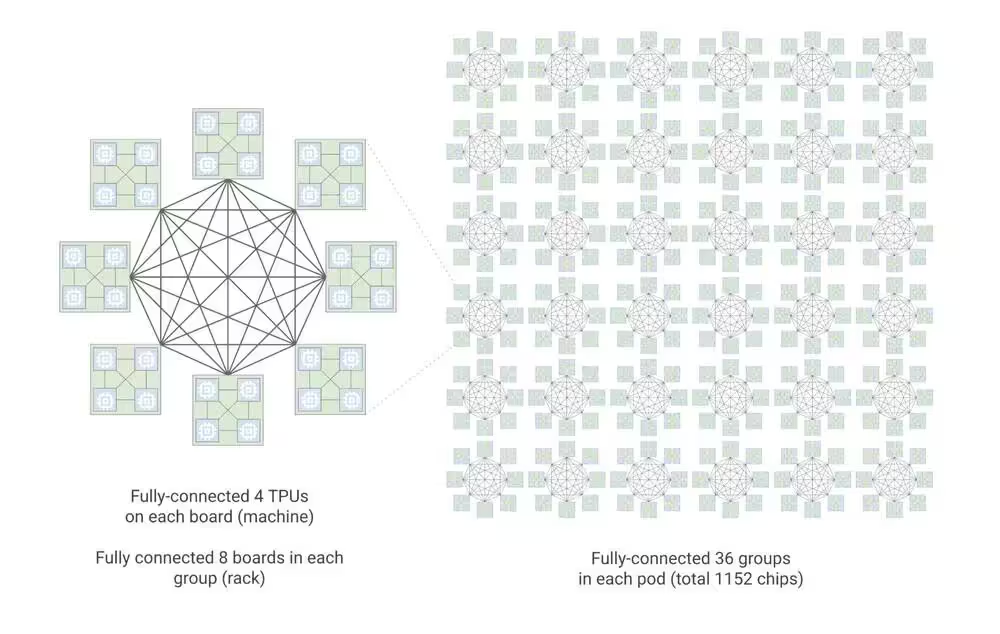

Le système s’appuie aussi sur des hôtes CPU Axion à architecture Arm conçus par Google. Le nombre d’hôtes physiques par serveur est doublé, avec une organisation mémoire de type NUMA pour l’isolation. Sur les modèles Mixture of Experts, la bande passante ICI grimpe à 19,2 Tb/s, tandis que la nouvelle topologie Boardfly réduit de plus de 50 % le diamètre maximal du réseau.

Google ajoute enfin un moteur d’accélération des collectives directement sur la puce, le Collectives Acceleration Engine, chargé de déporter les opérations globales et de réduire la latence on-chip jusqu’à 5 fois. Résultat annoncé : 80 % de performance par dollar en plus face à Ironwood, ce qui permettrait de servir presque deux fois plus de clients à coût identique.

Le design a d’ailleurs été explicitement calibré pour les besoins de Gemini et des modèles de raisonnement actuels : topologie Boardfly adaptée à leurs communications, capacité SRAM du TPU 8i dimensionnée pour l’empreinte du KV cache en production, et objectifs de bande passante du tissu Virgo dérivés des exigences d’entraînement à l’échelle du trillion de paramètres.

Axion, frameworks ouverts et contrainte énergétique

Pour la première fois, les deux puces s’appuient sur le même hôte Axion Arm maison. Google y voit un moyen d’optimiser non seulement l’accélérateur, mais l’ensemble de la plateforme. Les TPU 8t et 8i prennent en charge nativement JAX, MaxText, PyTorch, SGLang et vLLM, avec un accès bare metal sans surcouche de virtualisation. Google cite aussi ses contributions open source, notamment les implémentations de référence MaxText et Tunix pour le reinforcement learning.

Sur l’efficacité énergétique, Google annonce jusqu’à 2 fois plus de performance par watt que la génération Ironwood. Le groupe insiste sur une approche système, en intégrant notamment le réseau et le calcul sur la même puce pour réduire le coût énergétique des transferts de données au sein des pods. Ses centres de données auraient, au passage, gagné un facteur 6 en puissance de calcul par unité d’électricité sur les cinq dernières années.

Les deux plateformes reposent enfin sur une technologie de refroidissement liquide de quatrième génération, jugée nécessaire pour tenir des densités de performance qu’un refroidissement à air ne pourrait pas soutenir durablement.

Google indique que les TPU 8t et 8i seront disponibles de manière générale plus tard dans l’année via son offre AI Hypercomputer. Citadel Securities dit déjà avoir obtenu avec les TPU Ironwood de septième génération des charges exécutées 2 à 4 fois plus vite et à un coût inférieur de 30 %, et compte basculer vers les nouvelles architectures pour aller plus loin sur l’économie d’entraînement et l’échelle.

Ce lancement illustre surtout un basculement plus large du marché : l’inférence devient une cible d’ingénierie aussi stratégique que l’entraînement. En séparant clairement les rôles entre TPU 8t et TPU 8i, Google admet qu’à l’échelle des grands modèles et des agents, la latence mémoire, l’interconnexion et le coût par requête comptent désormais autant que les ExaFlops affichés.

Source : TechPowerUp