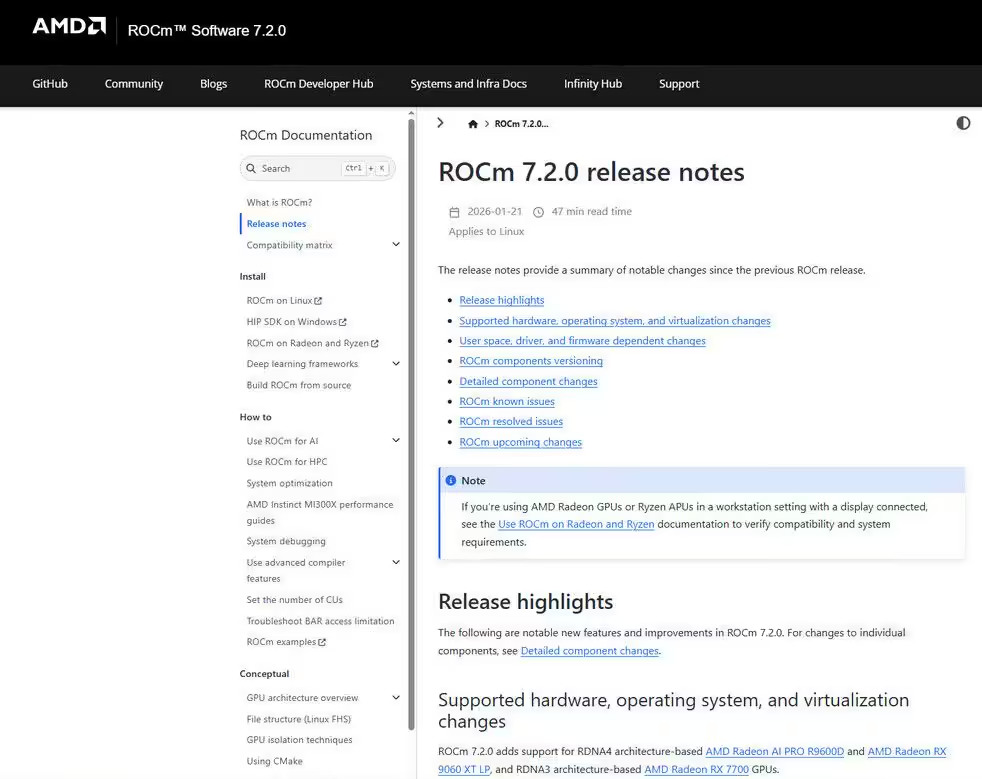

ROCm 7.2 frappe là où ça compte : performances, efficacité et fiabilité pour l’IA moderne. Dès cette version, ROCm 7.2 pousse les GPU AMD Instinct plus loin avec du FP8/FP4, un tuning GEMM musclé et une communication GPU‑GPU allégée du CPU.

ROCm 7.2 : perfs GEMM, nouvelles données FP8/FP4 et réseau plus intelligent

hipBLASLt gagne des fonctions ciblées pour les charges GEMM : capacités de tuning élargies, « restauration depuis logs » pour rejouer une configuration performante, swizzle A/B pour optimiser les accès mémoire, ainsi que des rapports et benchmarks plus lisibles. AMD évoque des gains mesurables sur les AMD Instinct MI200 et MI300 par rapport à ROCm 7.1.

Tuning GEMM généralisé sur FP8, BF16 et FP16, avec un focus sur des modèles concrets comme GLM‑4.6 et Llama 2. Sélection de kernels, tuilage, layouts mémoire et mouvements de données ont été ajustés pour coller aux formes et patrons d’exécution, avec à la clé plus de débit et moins de latence en entraînement et inférence.

rocMLIR et MIGraphX activent de nouveaux types bas‑précision FP8 et FP4. Fondation côté compilation, abaissement et exécution, pensée pour les workloads d’IA émergents et l’introduction des produits MI350. Objectif : maximiser performance et efficience, tout en préparant les architectures à venir.

Communication de bout en bout : rocSHMEM prend désormais en charge un backend GPUDirect Async (GDA) intra‑ et inter‑nœuds. Les GPU échangent directement, y compris via RNIC en RDMA, avec des kernels initiés côté device, retirant le CPU du chemin critique afin de réduire la latence. Côté RCCL, la pile devient topologie‑aware et exploite nativement les réseaux à 4 NIC : répartition des collectives sur plusieurs interfaces, alignement des rails pour limiter la contention et mieux saturer la bande passante. Des fonctions de NCCL 2.28 ont été rétro‑portées, apportant des collectives plus avancées et une montée en charge plus stable. AMD résume l’approche ainsi : « des collectives plus rapides et plus stables ».

ThinLTO arrive dans l’infrastructure de compilation pour GPU AMD

Le support ThinLTO permet des optimisations inter‑fichiers sans les temps de build d’un LTO complet. Inlining, spécialisation, élimination de code mort à l’échelle globale, avec une vitesse proche d’une compilation locale. Intérêt direct pour PyTorch, Triton, XLA et les piles de kernels maison.

Sécurité, virtualisation et gestion de puissance sur MI350X/MI355X

SR‑IOV et RAS activés sur MI350X et MI355X : évitement des bad pages pour maintenir la disponibilité GPU en cas de fautes mémoire, durcissement sécurité avec effacement de la mémoire volatile et protections contre le fuzzing MMIO, et parité fonctionnelle face aux plateformes concurrentes. Des capacités essentielles pour les déploiements cloud et entreprise multi‑locataires, avec meilleure isolation et fiabilité.

Optimisations modèles IA : sur MI355X et MI350X, Llama 3.1 405B reçoit des optimisations au niveau kernel et bande passante mémoire ; Llama 3 70B et Llama 2 70B sont également ajustés pour tirer parti de l’architecture. Sur la série MI300X, AMD a soigné les optimisations GEMM pour GLM‑4.6 et amélioré DeepEP pour une exécution plus rapide et une meilleure utilisation GPU.

Node Power Management : la gestion de puissance par nœud ajuste dynamiquement les fréquences GPU pour rester dans une enveloppe énergétique définie, via télémétrie embarquée et algorithmes de contrôle. Vérifiable dans AMD SMI. Pris en charge sur MI355X et MI350X, en bare‑metal et KVM SR‑IOV, avec PLDM bundle 01.25.17.07.

Source : TechPowerUp