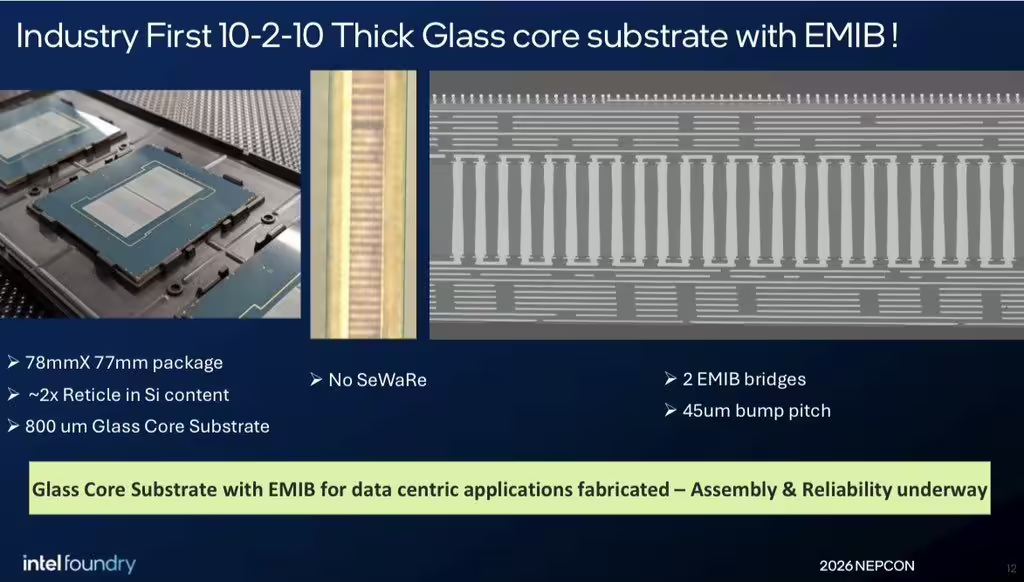

Intel a montré pour la première fois un prototype de substrat en verre intégrant EMIB lors de NEPCON Japan 2026 : un monstre de 78 x 77 mm, soit environ deux fois la surface d’un champ de réticule standard. L’objectif est clair : soutenir des architectures multi-puces massives pour l’IA en contournant les limites physiques des substrats organiques.

Verre plutôt que résine : des raisons mécaniques et lithographiques

Le passage au verre répond aux déformations des substrats organiques à haute température, sources de voilage et de défauts d’assemblage. Le coefficient de dilatation du verre, proche de celui du silicium, stabilise la coplanarité en thermique. Sa planéité intrinsèque autorise en outre des motifs plus fins pour les interconnexions, un point devenu critique avec des puces AI aux bords du « reticle limit ».

Le prototype présenté adopte un cœur en verre de 800 μm d’épaisseur, flanqué d’une pile « 10-2-10 » de couches de redistribution : 10 RDL au-dessus, 10 en dessous, soit 22 couches en tout avec le cœur, pour diriger des flux I/O très denses. Intel annonce un pas de micro-bumps de 45 μm, nettement plus agressif que les substrats organiques actuels.

EMIB validé, contraintes de fiabilité adressées

Deux ponts EMIB sont intégrés dans cette démo, confirmant la compatibilité du verre avec des topologies multi-dies complexes. Outre le resserrement des interconnexions, Intel met en avant un meilleur contrôle de profondeur de foyer et une réduction des contraintes mécaniques sur le package grâce à l’inertie du « thick core » 800 μm, pensée pour les environnements data center.

Point sensible, le « No SeWaRe » affiché par Intel cible les microfissures liées au sciage et à la manutention des substrats en verre, souvent fatales en cyclage thermique. Le message est que les procédés matière et process ont été suffisamment durcis pour atteindre une fiabilité de niveau production, verrou indispensable avant toute montée en volume.

Si la bascule vers le verre se confirme, elle rebattra les cartes du packaging avancé côté serveurs et accélérateurs AI. Des pitches à 45 μm et des surfaces de package au-delà du champ de réticule ouvrent la voie à des agencements chiplet plus denses et à des interconnexions latérales à plus faible latence, tout en transférant la complexité vers les chaînes d’assemblage et de test. Les fournisseurs de substrats, d’outillage de découpe et de métrologie seront en première ligne pour adapter leurs procédés à l’inertie mécanique et aux exigences de propreté du verre à grande échelle.

Source : ITHome