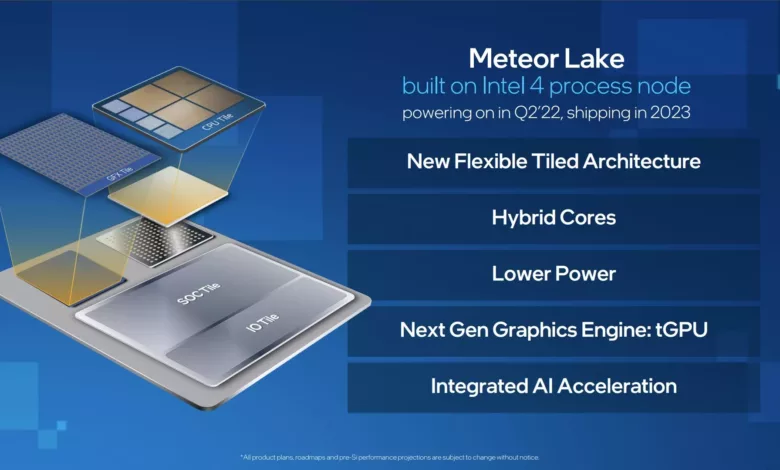

Les prochains processeurs mobiles Meteor Lake et Arrow Lake d’Intel introduisent un nouveau concept de chiplet. Auparavant représentée sous forme de blocs IP à l’aspect vague. Les nouvelles diapositives de la puce publiées par Intel mettent en lumière une approche à trois puces. Une organisation qui rappelle le MCM Ryzen Vermeer. Deux puces de cœur de CPU (CCD) communiquant avec une puce d’E/S client (cIOD), qui gère toute la connectivité du SoC. La conception d’Intel présente une différence majeure, à savoir une puce graphique intégrée. Apparemment, le MCM d’Intel utilise un processeur graphique intégré à côté du cœur du CPU et du processeur d’E/S (SoC). Intel aime appeler ses chiplets des « tuiles », et nous allons donc nous en tenir à cela.

Différentes gravures pour chaque puce

La tuile graphique, la tuile CPU et la tuile SoC ou E/S sont construites sur trois gravures différentes. En fonction du degré de besoin du nœud de processus le plus récent. Les nœuds utilisés sont Intel 4 ; optiquement 7 nm EUV, mais avec les caractéristiques d’un nœud de classe 5 nm. Intel 20A (caractéristiques de 2 nm), et le nœud externe TSMC N3 (3 nm). À ce stade, nous ne savons pas quelle tuile reçoit quoi. D’après ce que l’on peut voir, la dalle CPU possède une architecture hybride composée de P-cores « Redwood Cove » et de E-core « Crestmont ».

La tuile graphique intègre un iGPU basé sur l’architecture graphique Xe LP. Mais elle exploite un nœud avancé pour augmenter de manière significative le nombre d’unités d’exécution (EU) à 352. Et éventuellement augmenter les fréquences de fonctionnement. La tuile SoC et E/S comprend le processeur de sécurité de la plateforme, le northbridge intégré, les contrôleurs de mémoire, le complexe racine PCI-Express et les diverses E/S de la plateforme.

Intel prépare « Meteor Lake » pour un lancement en 2023, le développement devant s’achever en 2022. Mais la production en série pourrait encore commencer l’année prochaine.

Source : Intel

Retrouvez l’actualité hardware ici