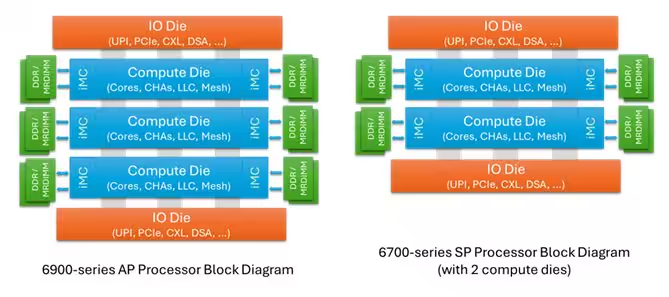

Intel vient de confirmer via des patches du noyau Linux que les processeurs Xeon « Diamond Rapids » adoptent une architecture modulaire avec séparation des rôles : des puces CBB (Core Building Block) pour le calcul et des puces IMH (Integrated I/O & Memory Hub) pour l’I/O et le contrôleur mémoire. Information repérée par ITHome via leaker @InstLatX64.

Architecture CBB/IMH et contrôleur mémoire séparé

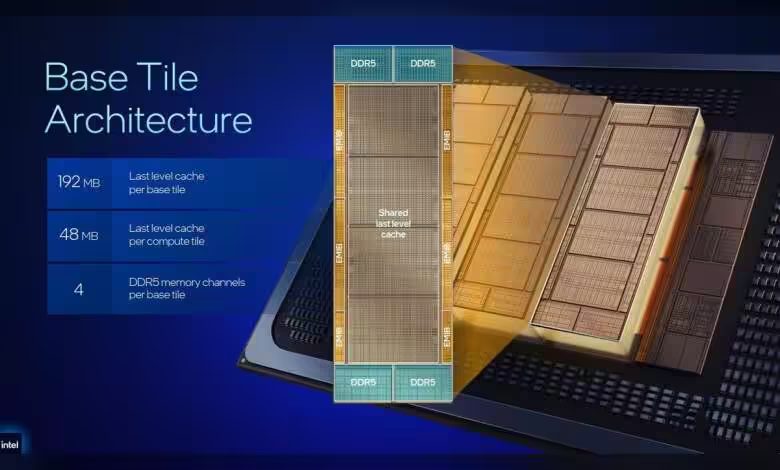

Contrairement à Granite Rapids, Diamond Rapids déporte le contrôleur mémoire sur une puce IMH dédiée, isolant physiquement calcul, I/O et sous-système mémoire. Jusqu’à deux puces IMH peuvent accompagner le ou les CBB, avec un placement sur le substrat rappelant Clearwater Forest.

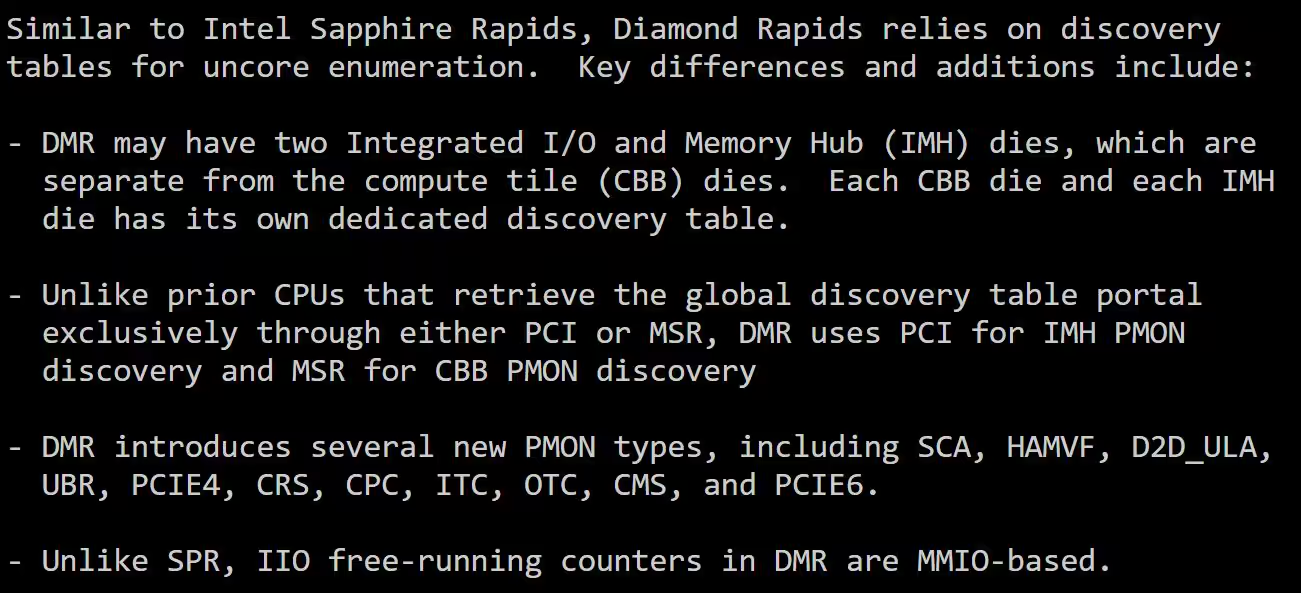

Chaque CBB et chaque IMH expose sa propre « table de découverte » pour l’énumération, dans la lignée de Sapphire Rapids mais avec une répartition par composant. La télémétrie PMON distingue les chemins: découverte/monitoring IMH via PCI, et CBB via MSR. De nouveaux types PMON font leur apparition (SCA, HAMVF, D2D_ULA, UBR, PCIE4, CRS, CPC, ITC, OTC, CMS, PCIE6). Les compteurs IIO « free-running » migrent vers une implémentation basée sur MMIO.

PCIe 6.0 et objectifs de cœurs élevés

Diamond Rapids ajoute le support de PCIe Gen6, aligné avec les futures plateformes data center comme Venice. Les fuites évoquent jusqu’à 192 cœurs (des rumeurs poussent jusqu’à 256), des P-cores Panther Cove sur procédé Intel 18A, et un TDP maximal de 650 W sur plateforme LGA 9324 multi-socket.

Intel vise une fenêtre de lancement au milieu ou au second semestre 2026. Comme toujours, ces indications restent tributaires de l’évolution du silicium et des microcodes.

Source : ITHome