Le CXL Consortium passe la surmultipliée avec CXL 4.0 et vise clairement les charges IA et HPC : la nouvelle spécification double le débit et muscle la connectivité mémoire cohérente des data centers.

CXL 4.0 double la vitesse et élargit l’écosystème

Le standard Compute Express Link franchit une étape majeure avec un débit porté à 128 GT/s sans latence ajoutée. D’après l’organisme, ce bond de bande passante accélère directement les échanges entre dispositifs CXL et conserve les optimisations de protocole introduites en 3.x via le format de flit 256 octets. Derek Rohde, président du consortium et ingénieur principal chez Nvidia, résume l’enjeu : « la sortie de CXL 4.0 fixe un nouveau cap pour la connectivité mémoire cohérente ».

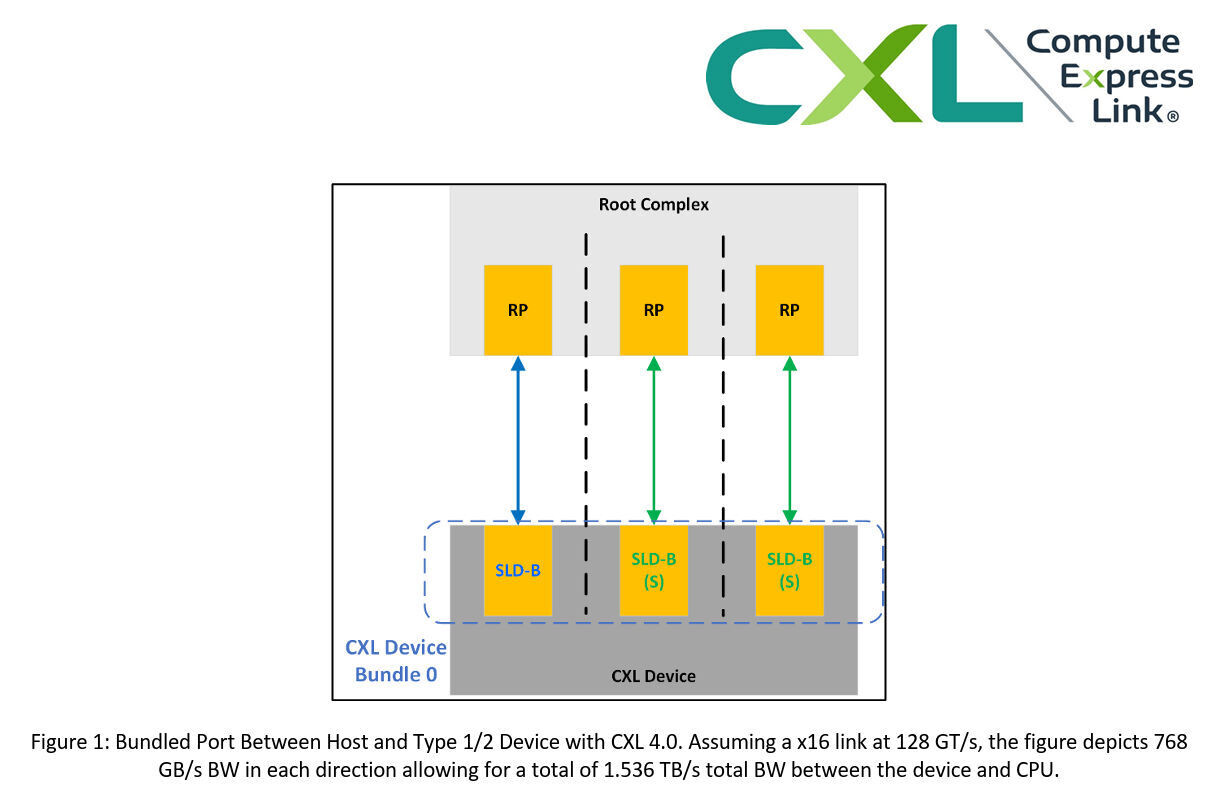

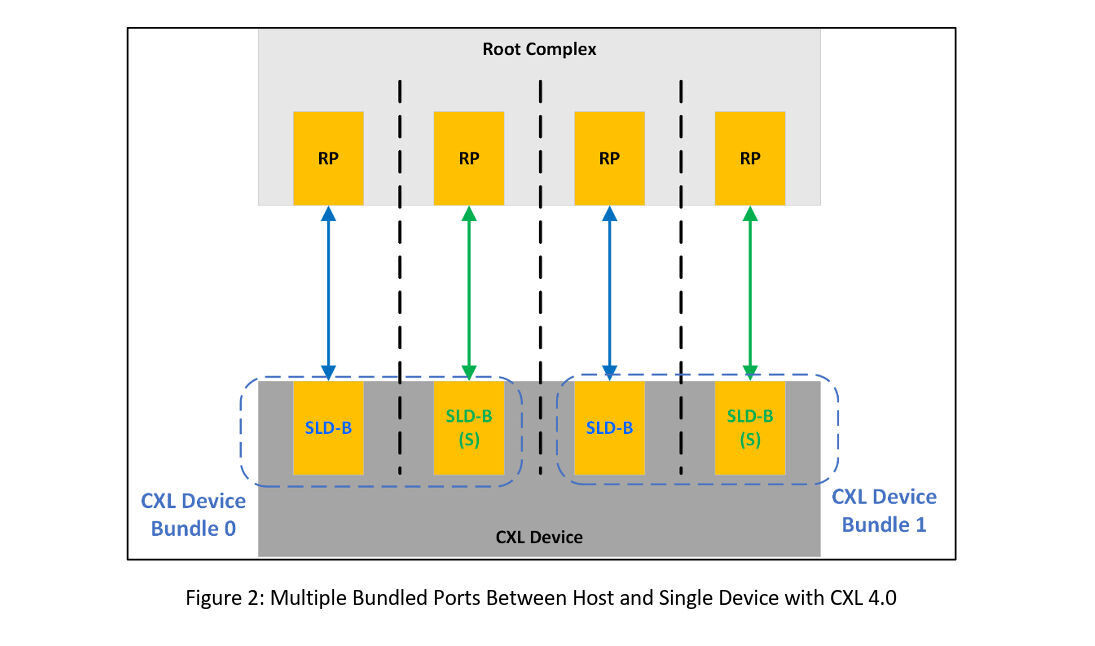

Au chapitre des nouveautés techniques, CXL 4.0 introduit le mode x2 natif afin d’augmenter le fan-out au niveau plateforme, et autorise jusqu’à quatre retimers pour étendre la portée des canaux. La spécification inaugure aussi la capacité de ports groupés : il devient possible d’agréger des ports entre l’hôte et des accélérateurs CXL de type 1/2 pour accroître le débit de la liaison.

Le volet fiabilité n’est pas oublié avec des améliorations RAS mémoire, destinées à mieux tracer les erreurs et rationaliser la maintenance. Comme attendu, la rétrocompatibilité est totale avec CXL 3.x, 2.0, 1.1 et 1.0, de quoi faciliter les déploiements progressifs dans les baies existantes.

Feuille de route écosystème : démos à SC’25 et webinaire

Le consortium prévoit des démonstrations au CXL Pavilion (stand 817) lors de Supercomputing 2025, du 16 au 21 novembre à St. Louis. Une session « Birds of a Feather » abordera l’exploitation du pooling et du partage de mémoire CXL pour les charges IA et HPC, mardi 18 novembre de 12 h 15 à 13 h 15, heure du Pacifique.

Pour aller plus loin, une présentation en ligne gratuite est programmée le jeudi 4 décembre à 8 h, heure du Pacifique, afin de détailler les nouveautés de CXL 4.0.

Source : TechPowerUp