Bref

AMD prépare une rupture avec Zen 6 en abandonnant le SERDES pour un interconnect parallèle “Sea-of-Wires”, déjà testé dans Strix Halo via la technologie InFO-oS de TSMC. Ce changement réduit la consommation et la latence tout en augmentant la bande passante. Une étape majeure qui s’inscrit aux côtés des avancées comme la gravure en 2 nm N2P et l’arrivée des APU Medusa Point.

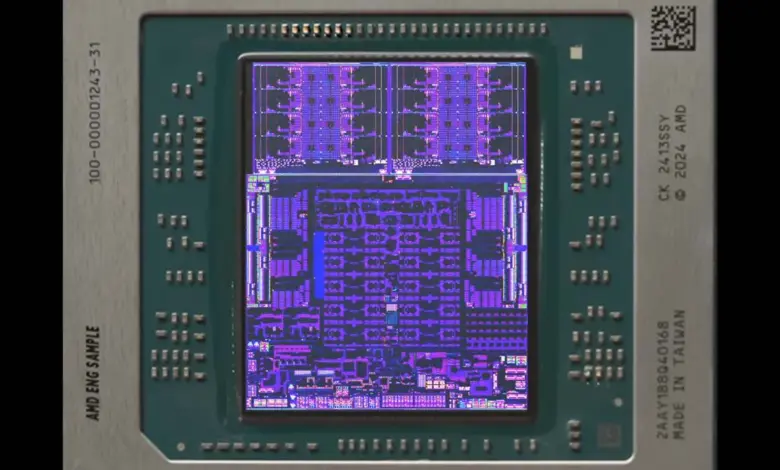

AMD s’apprête à franchir un cap majeur avec Zen 6. Après avoir exploité la technologie SERDES depuis Zen 2 pour relier ses différents dies, l’entreprise inaugure une approche radicalement différente : le “Sea-of-Wires”. Déjà observée dans les APU Strix Halo, cette innovation s’appuie sur l’InFO-oS de TSMC pour répondre aux limites en latence et en consommation, devenues critiques à l’ère des NPU et du calcul hétérogène.

Les limites du SERDES chez AMD

Le SERDES, adopté depuis Zen 2, reposait sur des transmissions série haut débit. Efficace dans les débuts, il est aujourd’hui un frein. Deux points posent problème :

- un coût énergétique élevé dû au codage/décodage et à la récupération d’horloge,

- une latence accrue liée à la conversion série/parallèle.

Avec des charges de travail massivement parallèles, ces contraintes deviennent rédhibitoires, que ce soit pour les CPU grand public ou les serveurs EPYC Venice jusqu’à 256 cœurs.

Strix Halo, premier laboratoire du changement

Les APU Strix Halo ont servi de terrain d’expérimentation. Les ingénieurs ont observé un basculement progressif vers un interconnect parallèle via InFO-oS (Integrated Fan-Out on Substrate). Grâce à une couche de redistribution (RDL), il est possible de multiplier les connexions courtes et fines entre blocs de calcul et SoC.

Résultat : une communication via de larges ports parallèles, sans étape de conversion série/désérialisation.

Les bénéfices du “Sea-of-Wires”

En éliminant la conversion, cette approche offre trois avantages clairs :

- consommation réduite grâce à des transmissions directes,

- latence nettement diminuée,

- bande passante évolutive par simple ajout de lignes parallèles.

Ces atouts se combinent aux autres innovations de Zen 6, notamment la gravure en 2 nm N2P et le futur socket FP10 pour Medusa Point, confirmant une génération pensée pour l’IA et les GPU intégrés.

Des contraintes techniques à gérer

L’approche fan-out complique le design : routage plus complexe, espace sous les dies encombré. Pourtant, le gain global reste décisif, surtout pour des architectures hybrides comme AMD Medusa Halo avec 26 cœurs Zen 6 et iGPU RDNA 5, où la communication rapide entre blocs est critique.

Zen 6, la généralisation du modèle

Tout indique qu’AMD généralisera cette approche dans Zen 6. Après l’expérimentation Strix Halo, l’entreprise semble prête à imposer le “Sea-of-Wires” comme nouveau standard, au même titre que l’organisation en chiplets l’avait été avec Zen 2.

Ce choix pourrait aussi bénéficier aux futurs APU custom, comme ceux des consoles next-gen à base de Zen 6 et RDNA 5 dans Xbox Magnus, où chaque gain en latence est crucial pour atteindre les 4K/120 FPS.

Conclusion

Avec Zen 6, AMD ne se contente pas d’une optimisation incrémentale. Le passage du SERDES au “Sea-of-Wires” constitue une rupture dans la conception des processeurs. Associée à la gravure 2 nm, au socket FP10 et à l’arrivée de Medusa Point, cette stratégie place AMD en position de force face aux workloads IA et aux besoins croissants de bande passante des consoles et serveurs.