Alors que nous commençons à peine à apprivoiser Zen 5, une fuite d’ampleur vient déjà lever le voile sur la suite. Un document technique officiel d’AMD, destiné aux développeurs, détaille l’architecture Zen 6 et esquisse une évolution majeure : un moteur de calcul élargi à 8 slots, capable de redistribuer beaucoup plus d’instructions par cycle. De quoi redéfinir le niveau de performance attendu sur PC dans les années à venir, possiblement dès 2026.

Cette révélation s’inscrit dans un contexte plus large, alors qu’AMD a déjà confirmé Zen 6 en 2 nm tout en préparant Zen 7, laissant entrevoir une accélération nette de sa feuille de route CPU.

AMD Zen 6 se dévoile en coulisses : une microarchitecture taillée pour le calcul massif

Une documentation technique officielle destinée aux développeurs, récemment repérée, offre un premier aperçu détaillé de la future microarchitecture. Derrière un titre austère et sans la moindre mention commerciale se cache pourtant un changement profond dans la façon dont les cœurs Zen traiteront les instructions.

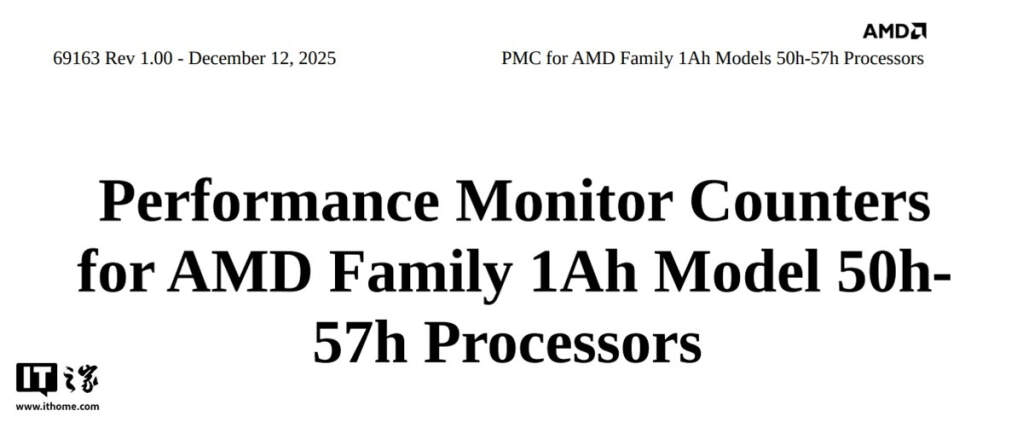

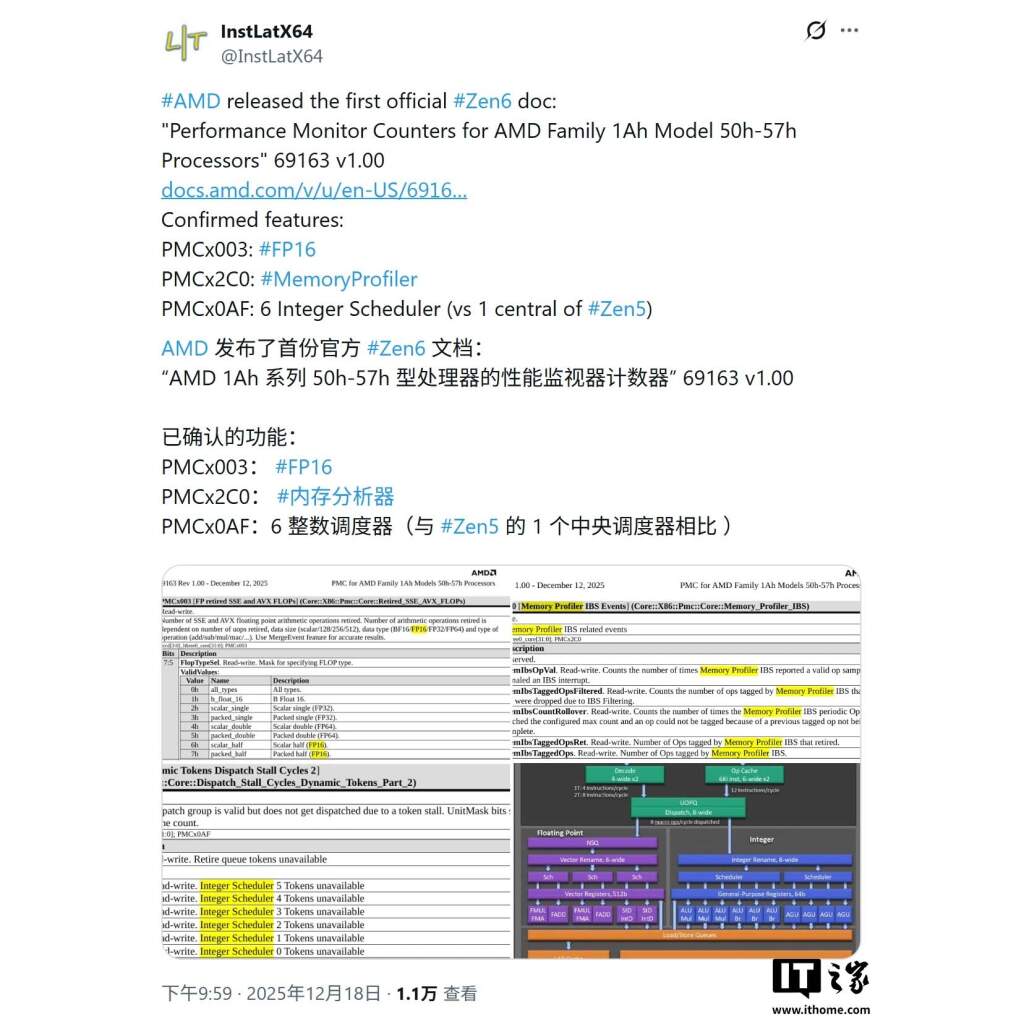

Le document, référencé comme AMD Family 1Ah Model 50h–57h Processor Performance Monitoring Counters, décrit de nouveaux compteurs de performance internes. Leur existence permet, en creux, de reconstituer l’organisation du cœur Zen 6 et d’identifier plusieurs évolutions majeures, à commencer par un élargissement significatif du front-end.

Un cœur Zen 6 plus large et plus agressif

Le dispatch passe à 8 slots

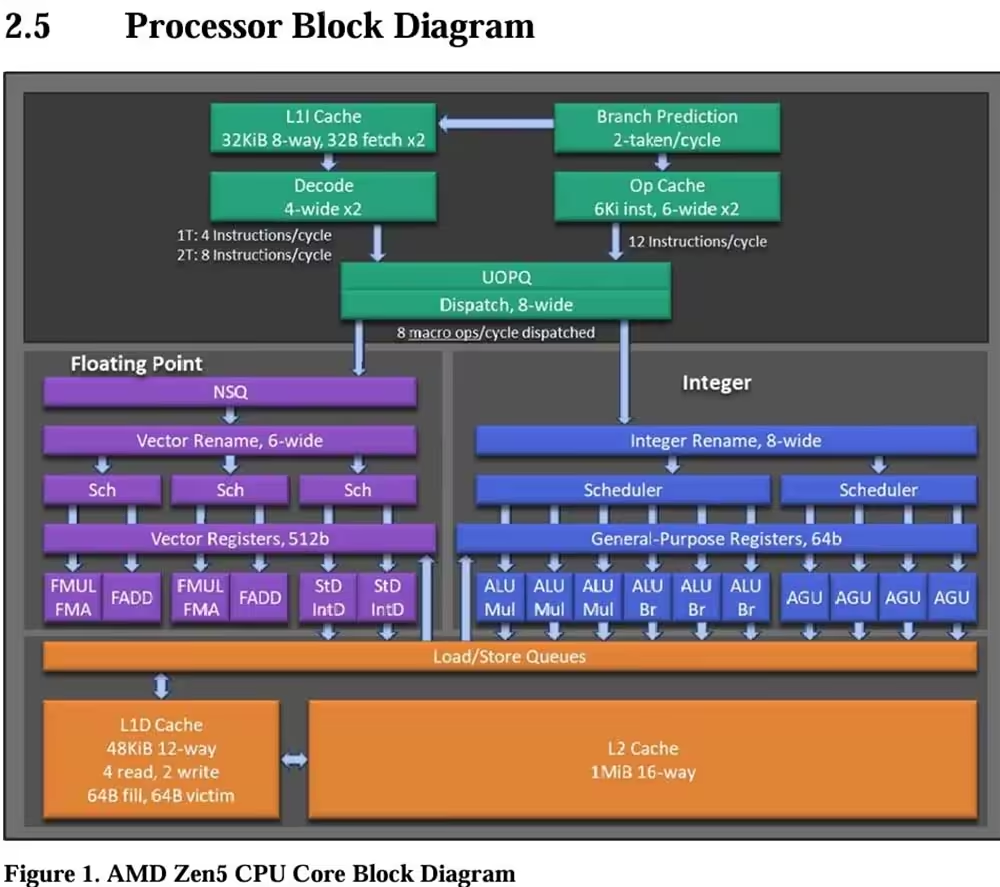

La révélation la plus marquante concerne l’étage de dispatch. Zen 6 adopte une unité de distribution à 8 slots, contre 6 sur les générations Zen actuelles. Concrètement, cela signifie que le processeur pourra envoyer davantage d’instructions par cycle vers les unités d’exécution. Ce type d’évolution n’est jamais anodin : il implique une refonte en profondeur du pipeline, des buffers internes et de la gestion des dépendances.

Un dispatch plus large permet d’augmenter le débit d’instructions en conditions idéales, mais surtout de mieux exploiter les ressources lorsque le code présente suffisamment de parallélisme. Cette évolution fait écho à la refonte de l’interconnexion interne Sea-of-Wires, pensée pour réduire la latence et améliorer l’efficacité globale.

Une meilleure exploitation du parallélisme interne

Avec 8 slots, Zen 6 se rapproche d’architectures historiquement plus agressives sur le plan du front-end. L’objectif n’est pas uniquement d’augmenter les performances maximales, mais aussi de réduire les phases de sous-utilisation des unités d’exécution. Moins de bulles dans le pipeline, c’est un meilleur rendement énergétique et un gain de performances plus régulier, y compris hors benchmarks synthétiques.

SMT toujours de la partie, mais mieux instrumenté

Le multithreading simultané est maintenu

La documentation confirme également que Zen 6 conserve le SMT. AMD continue donc de faire confiance à cette approche pour améliorer l’occupation des ressources et les performances en multitâche. Rien d’étonnant à cela, mais le point intéressant se situe ailleurs : dans la finesse de l’observation.

Les nouveaux compteurs exposés permettent de suivre avec précision la manière dont les threads se partagent les ressources internes. Attentes dans le pipeline, conflits d’accès, saturation de certaines unités : tout devient mesurable. Cela donne aux développeurs des outils précieux pour comprendre où se situent les véritables goulots d’étranglement et adapter leurs optimisations à une architecture plus large et plus complexe.

Zen 6 change de dimension côté calcul

Le support explicite des instructions 512 bits

Autre élément clé du document : la prise en charge d’instructions 512 bits. AMD renforce clairement les capacités vectorielles et en calcul flottant de Zen 6. Cette évolution aligne davantage l’architecture sur les besoins modernes en calcul scientifique, traitement multimédia et charges professionnelles intensives.

IA, chiffrement et charges spécialisées en ligne de mire

La présence d’instructions comme VNNI pour l’IA, ainsi que les extensions AES et SHA pour le chiffrement et le hashing, montre une orientation très nette. Zen 6 n’est pas seulement pensé pour le desktop grand public, mais pour des usages où le CPU reste central malgré la montée en puissance des accélérateurs dédiés.

Une vision encore incomplète, mais déjà très parlante

À ce stade, aucun nom commercial, aucun calendrier et aucun benchmark ne figurent dans la documentation. Impossible donc de savoir quand Zen 6 arrivera sur le marché ou comment il sera décliné entre desktop, mobile et serveur. En revanche, les premières indications côté plateforme AM5 se veulent rassurantes.

Une évolution majeure dans la philosophie Zen

Avec Zen 6, AMD semble préparer un véritable changement de rythme. Front-end élargi, calcul vectoriel renforcé, instrumentation plus fine du SMT : tout indique une architecture pensée pour durer et pour encaisser les charges de travail des prochaines années, notamment dans l’IA et le calcul intensif.

Ce premier aperçu ne dit pas tout, mais il suffit déjà à comprendre une chose : Zen 6 ne sera pas une simple itération. C’est une montée en gamme structurelle, et probablement l’une des évolutions les plus ambitieuses de l’architecture Zen depuis ses débuts.