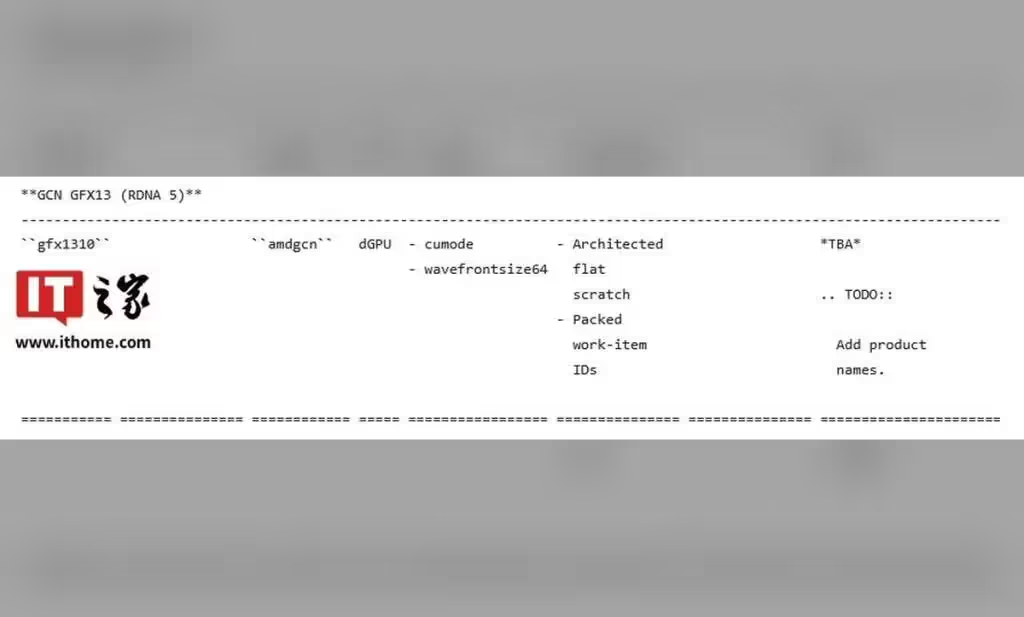

Une nouvelle entrée « gfx1310 » a fait son apparition dans le dépôt LLVM, confirmant l’amorçage du support pour un GPU AMD de la famille GFX13, autrement dit RDNA 5, et identifié comme une carte graphique dédiée. Ce type d’atterrissage dans l’infrastructure du compilateur précède habituellement les phases de validation interne des pilotes et l’écosystème toolchain, et marque un jalon concret côté logiciel.

Le libellé « gfx1310 » s’inscrit dans la nomenclature AMD où GFX10, 11 et 12 correspondent respectivement à RDNA, RDNA 2 et RDNA 3/3.5. GFX13 est donc le premier indicateur opérationnel d’une bascule RDNA 5 dans les chaînes de compilation. Le code repéré suggère une cible dGPU et non une intégration iGPU, ce qui oriente vers les futures cartes grand public et professionnelles dédiées.

Des fuites antérieures évoquaient des puces RDNA 5/« UDNA » avec jusqu’à 96 unités de calcul et un bus mémoire jusqu’à 512 bits. Ces paramètres n’apparaissent pas dans LLVM et doivent rester considérés comme non confirmés. En revanche, la présence dans LLVM implique que les identifiants matériels et certaines caractéristiques ISA commencent à être figés pour la chaîne de compilation.

Ce que change l’arrivée de « gfx1310 » dans LLVM

L’ajout d’un nouveau target dans LLVM ouvre la voie à l’alignement des pilotes open source (Mesa/ROCm) et aux optimisations spécifiques de l’ISA RDNA 5 côté shader et compute. Les développeurs peuvent commencer à câbler les chemins de compilation, à intégrer les premiers passes d’optimisation et à préparer le support dans les piles graphiques et GPGPU.

Le rythme habituel veut que ces commits précèdent de plusieurs mois toute annonce produit. À ce stade, aucune donnée chiffrée issue du dépôt ne valide les configurations mémoire ou le nombre de cœurs, mais le positionnement « dGPU » laisse augurer un die dédié et non une déclinaison APU.

Si AMD verrouille effectivement un bus 512 bits sur au moins une référence RDNA 5, l’écosystème compiler/pilotes devra intégrer des chemins spécifiques de gestion de bande passante et de hiérarchies de cache, avec des impacts directs sur le scheduling et la coalescence mémoire. C’est typiquement ce que ces premiers commits LLVM permettent d’anticiper côté toolchain, bien avant les benchmarks publics.

Source : ITHome