AMD a confirmé de nouveaux détails sur sa nouvelle technologie 3D V-Cache utilisée par la série Ryzen 7000X3D.

Près d’une semaine s’est écoulée depuis le lancement de la série Ryzen 7000X3D. AMD a été transparent et a fourni tous les détails nécessaires que les consommateurs auraient pu vouloir savoir. Cependant, il y avait encore quelques détails qui n’étaient peut-être pas aussi importants pour les utilisateurs finaux. Mais qui restaient néanmoins très intéressants pour la communauté technologique.

Au cours du week-end, AMD a fourni de plus amples détails sur la technologie 3D V-Cache. La marque a publié la toute première image de la nouvelle matrice d’E/S. Le troisième chiplet accompagnant les processeurs grand public à deux 8 cœurs, dont le nom de code est Raphael. Suite à la demande de Tom’s Hardware, AMD a dévoilé certains de ces détails. Tandis que les autres détails sont arrivés lors de la Conférence internationale des circuits à semi-conducteurs (ISSCC) de 2023.

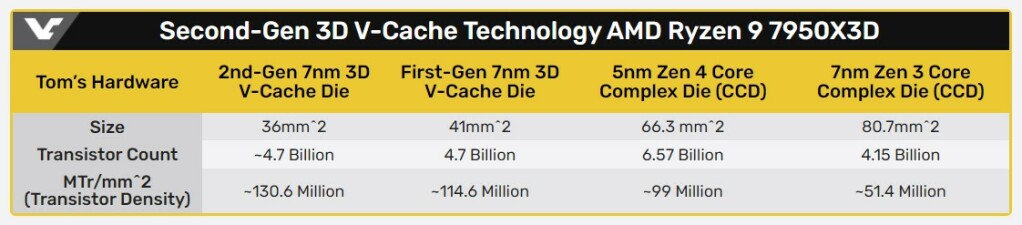

Le 3D V-Cache sur la série Ryzen 7000 étend le cache de niveau 3 jusqu’à 96 Mo pour l’un des chiplets. Le cache lui-même repose sur le nœud de processus 7nm, même s’il se trouve au-dessus du CCD Zen4 5nm. Le cache de deuxième génération est en fait plus petit que celui de première génération. Tout en conservant le même nombre de transistors. Cela signifie que la densité de transistors est passée de 114,6M à 130,6 MTr/mm².

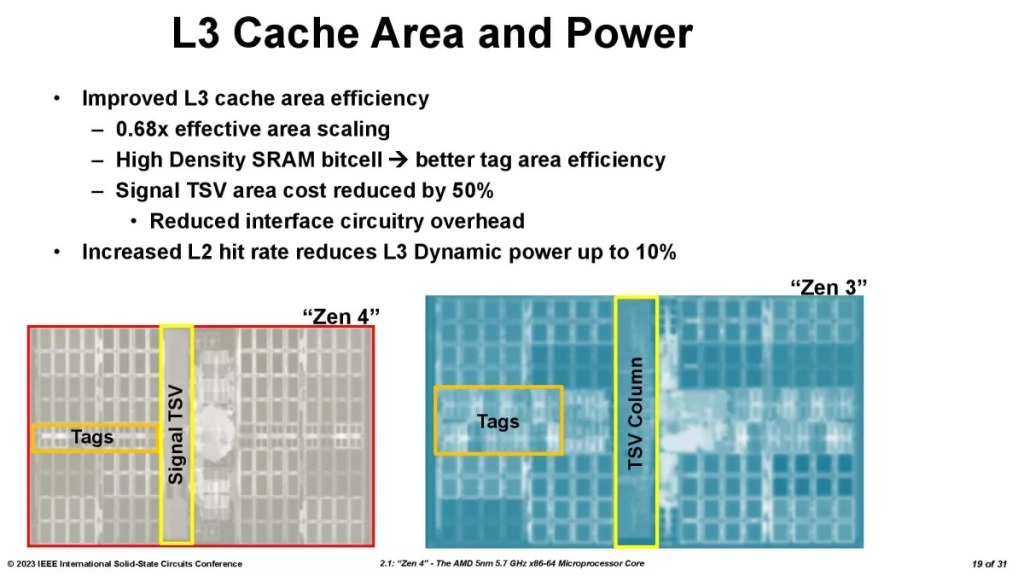

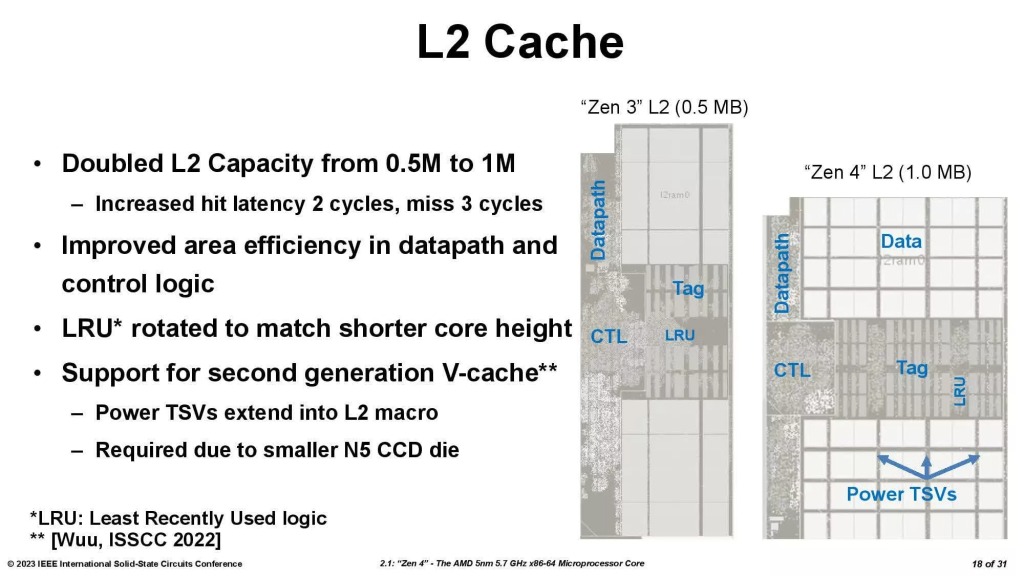

AMD a également confirmé que le nouveau cache a une bande passante plus élevée, atteignant 2,5 TB/s. Cela représente une amélioration de 25 % ou 0,5 TB/s par rapport à la conception du cache du 5800X3D. En outre, en raison des modifications apportées à la conception, AMD a dû modifier les connexions TSV (Through Silicon Vias). L’entreprise a dû réduire la surface des TSV de 50 %.

AMD utilise les mêmes CCD Zen4 sur les séries Ryzen et EPYC. Mais la matrice E/S est différente entre les processeurs grand public et ceux pour les environnements de centres de données. Une photo de la matrice d’E/S grand public est présente dans le diaporama de la présentation de l’ISSCC. Locuza s’est saisi de l’information pour y mener une analyse fine. Il montre la taille du GPU intégré et confirme qu’il est effectivement limité à 128 cœurs. Il est également confirmé que le chiplet d’E/S n’a que deux ports GMI (Global Memory Interconnect). Donc aucune configuration à triple CCD n’est possible avec ce chiplet.

Source : Videocardz, Tom’s Hardware, @Locuza, TechSpot

Retrouvez l’actualité hardware ici